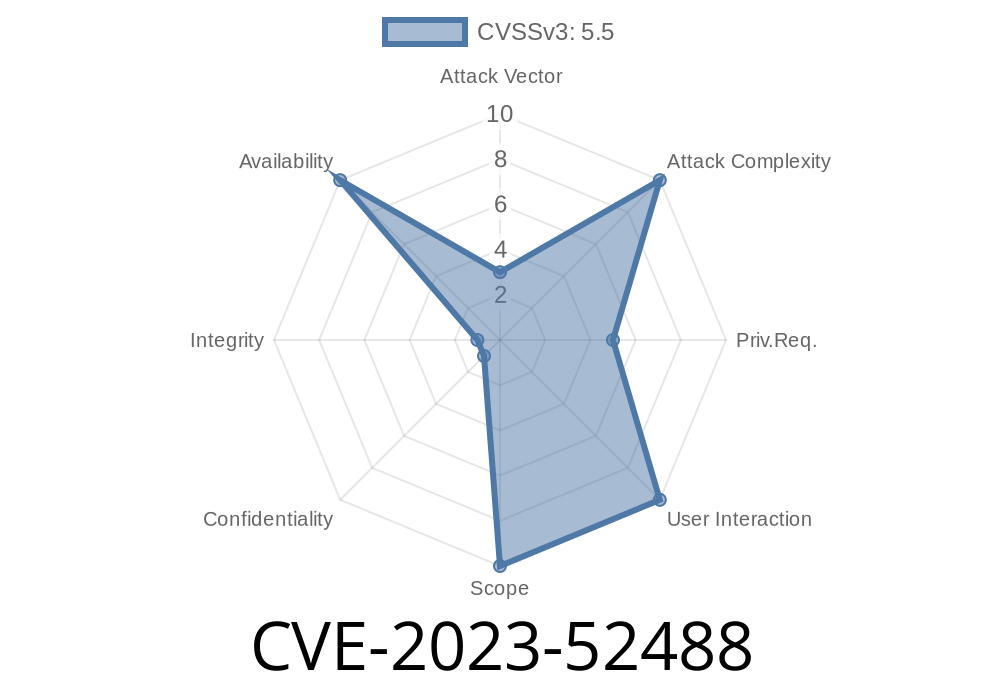

CVE-2023-52488 is a kernel vulnerability that affected Linux systems using the sc16is7xx serial chip driver. The issue stemmed from how the driver accessed the chip’s FIFO (First-In, First-Out) buffer using regmap helper functions. If you use this chip, especially on SPI buses, read on for details, code snippets, a simple explanation of the bug, and how it’s been fixed.

The Background: Serial Chips and Linux Drivers

The NXP SC16IS7XX is a serial communication IC, often used to provide UART (Universal Asynchronous Receiver/Transmitter) interfaces via I²C or SPI. Like many such chips, it uses an internal FIFO to buffer data.

Linux device drivers for these chips frequently use regmap, a powerful abstraction for register access. Regmap can cache register values to reduce I/O, and makes it easier to write generic driver code.

The SC16IS7XX supports burst mode for fast FIFO access.

- Burst mode requires sending the FIFO’s address once, then reading/writing multiple data bytes without incrementing the register address after each byte.

What Went Wrong?

The Linux driver wrongly used the _raw_ functions for FIFO burst operations.

- In typical use, _raw_ helpers update regmap’s cache as if each byte corresponded to a new (incremented) register.

// But for the FIFO, the register does not increment during a burst!

Code Snippet: The Buggy Approach

/* This is what the old code looked like */

ret = regmap_raw_read(dev->regmap, SC16IS7XX_REG_RHR, buf, len);

/* Or, for write: */

ret = regmap_raw_write(dev->regmap, SC16IS7XX_REG_THR, buf, len);

This would corrupt the regmap cache (if it wasn’t disabled by hand), as regmap assumes it’s writing to sequential registers!

Real-World Impact

The corruption wasn’t always visible. But if a developer enabled the cache (for performance), they would end up with bad data in the cache, possibly leading to unpredictable serial driver behavior or subtle data corruption. Not directly privilege escalation, but could break serial comms or cause system instability — always bad news for drivers interacting with external hardware.

The Fix: Using the Right Helpers

The solution was to switch to the _noinc_ regmap helpers. These functions do NOT increment the address, matching the chip’s actual FIFO burst mode. With this change, regmap’s cache is not affected, removing the need for manual cache disabling.

Code Snippet: The Correct Approach

/* The modern, correct method */

ret = regmap_noinc_read(dev->regmap, SC16IS7XX_REG_RHR, buf, len);

/* Or, for write: */

ret = regmap_noinc_write(dev->regmap, SC16IS7XX_REG_THR, buf, len);

Additionally, the FIFO registers are marked volatile, ensuring regmap never tries to cache them at all.

Who is vulnerable?

Any kernel version that used the buggy version of the driver and did not manually disable regmap cache for FIFO accesses.

How could this be exploited?

An attacker with control over the serial interface could trigger cache corruption in the driver, potentially breaking communication or (in rare cases) causing denial of service. Exploitation is tricky and would be highly targeted — but misbehaving or malicious hardware on a shared bus could cause mischief.

Proof of Concept?

For developers: Write/read more than 1 byte to FIFO using the old driver, enable regmap cache, and observe cache inconsistency after burst operation.

Use the correct regmap helpers for your hardware’s addressing mode.

- Beware “clever” workarounds (like manually disabling regmap cache) — chances are there’s an existing helper for your use case!

References

- Linux Kernel Patch Commit For This Fix (mainline)

- NXP SC16IS7XX Datasheet (PDF, See Section on FIFO)

- Linux regmap-noinc API Documentation

In Summary

CVE-2023-52488 was a subtle but important bug, caused by using the wrong regmap helpers for non-incrementing (burst) FIFO operations in the SC16IS7XX driver. The fix ensures reliable, cache-safe access to the chip’s serial FIFOs. If you maintain custom kernel code or vendor drivers, double-check your register access patterns!

Timeline

Published on: 03/11/2024 18:15:16 UTC

Last modified on: 02/14/2025 16:40:56 UTC